TAISC (Time-Annotated Instuction Set Computer) consist of a cross-platform MAC protocol compiler and execution engine. MAC protocols significantly impact wireless performance metrics such as throughput, energy consumption and reliability. Although the choice of the optimal MAC protocol depends on time-varying criteria such as the current application requirements and the current environmental conditions, today’s MAC protocols cannot be upgraded after deployment since their implementations are typically written in low level, hardware specific code that is hard to reuse on other hardware platforms (different radio chips and/or technologies). The TAISC framework offers an abstraction for hardware independent MAC protocol design and management. The framework consists of a cross-platform MAC protocol compiler and an execution engine. The solution allows to describe MAC protocols in a platform independent language (consisting of a radio platform independent instruction set), followed by a straightforward compilation step, yielding dedicated binary code, optimized for specific radio chips. The cross-compilation approach allows developers to design MAC protocols once, and then compile them for reuse on different radio platforms. To enable time-critical operation, the TAISC compiler adds exact time annotations to every instruction of the optimized binary code. The execution engine running on the radio platform, will execute the instructions with accurate time control thanks to the time annotation.

The overall TAISC workflow to develop and execute a MAC protocol is illustrated in the figure below and involves the following steps:

- Step 1: device-agnostic MAC protocol creation. First, the MAC protocol designer creates a high-level, platform independent radio program to describe the MAC logic using predefined commands (instructions) in a C-like language, either using high-level C syntax or using a more intuitive drag- and-drop interface. This human readable code consists of a sequence of commands that describe the generic behavior of the MAC protocol and is largely independent of hardware specifics of the final hardware platform.

- Step 2: device specific compilation. Next, this human-readable sequence is compiled by the TAISC compiler into efficient, device-specific binary byte code that can be executed by the TAISC execution engine running on the radio platform.

- Step 3: protocol dissemination. Afterwards, the byte code is wirelessly transmitted to the target hardware platform and added to the MAC application repository on the local TAISC execution engine.

- Step 4: MAC protocol execution. Finally, the TAISC core executes the byte code.

This approach has been successfully implemented for IEEE 802.15.4 MAC protocols on an embedded wireless sensor node (RM090, more info see: http://doc.ilabt.iminds.be/ilabt-documentation/wilabfacility.html).

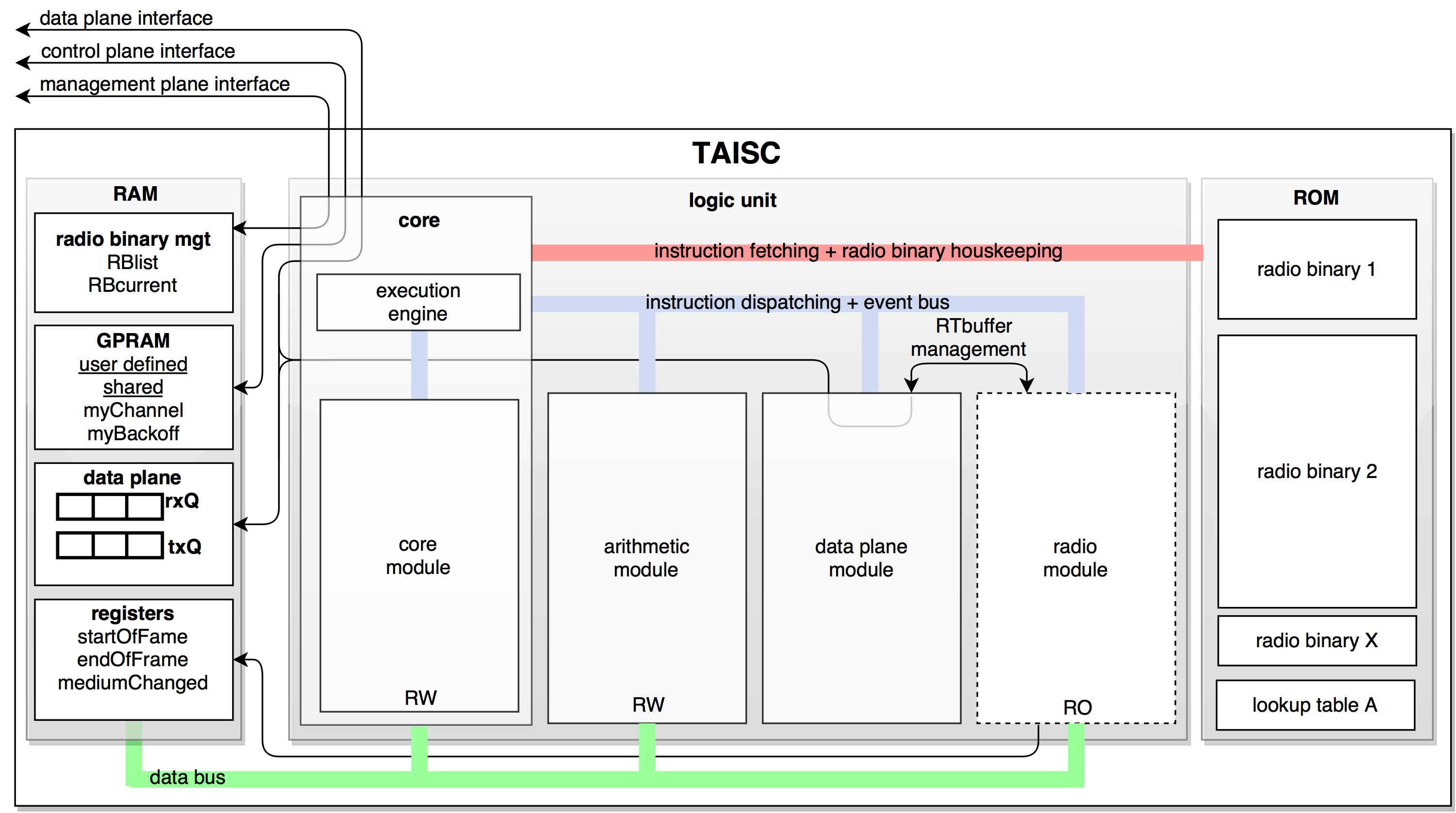

The full TAISC architecture is presented below:

The TAISC RAM unit (see left side in figure) contains dynamic information, including:

- radio binary management (keeps all the radio binaries consistent regarding their ROM and RAM boundaries and stores which radio binary is currently active)

- General Purpose RAM (GPRAM) for storing dynamic radio program variables

- access to the receive / transmit transmission queue

- TAISC registers that contain radio specific status information, such as the current radio frequency

The TAISC ROM unit (see right side in figure) stores static information, including one or more compiled radio programs as well as their static information such as lookup tables (for example to retrieve the radio frequency to use in each time slot for a hopping based MAC protocol).

The TAISC logic unit (see middle in figure) forms the core of the architecture. Its most important component is the execution engine that implements a scheduler which manages the execution times of the instructions, dispatches the instruction to the correct module, processes incoming events and schedules which instruction or radio program to fetch next. Instructions are executed by the core module (that a.o. manipulates the program counter for reacting to triggers or conditional events), the arithmetic module (supporting operations such as copy, add, subtract, etc.), the data plane module (that a.o. manages access to and from the data plane and manages conflicts between different modules) and the radio module (implementing chip specific radio implementations).

Finally, TAISC provides three upper layer interfaces (see upper left in figure): (i) the data plane interface interacts with incoming / received packets from higher layers, (ii) the control interface provides higher layers access to the radio program specific variables from the GPRAM and (iii) the management plane interface provides functionality to upload and/or activate new compiled MAC protocols.

The TAISC framework is available for experiments or extensions in the first Open Call in WiSHFUL.

Currently implemented MAC protocols are:

- CSMA/CA (Carrier Sense Multiple Access with Collision Avoidance)

- Single channel TDMA (Time Division Multiple Access)

- Channel hopping TDMA

- LPL (Low Power Listening)

Experimenters can control MAC protocols using the UPI interfaces (more info on GitHub)

Experimenters can develop their own MAC protocol using the cross-platform MAC protocol compiler.

Please contact imec (bart.jooris 'at' imec.be) if you need more information on TAISC or if you want to use the TAISC software. The TAISC software can be used free of charge for non-commercial academic purposes under a non-exclusive, non-assignable license.